围绕系统能力培养,构造递进式实验体系 全国大学生计算机系统能力大赛 —— 官方技术平台

支持自动评测的操作系统内核实验 查看详情

- 在线虚拟实验环境

-

借助虚拟机管理平台实现多节点实验服务器快速部署,避免了软件版本冲突问题,节约学生安装实验环境花费的时间,随时随地在线流畅使用。实验后能够长期保存学生实验过程资料。

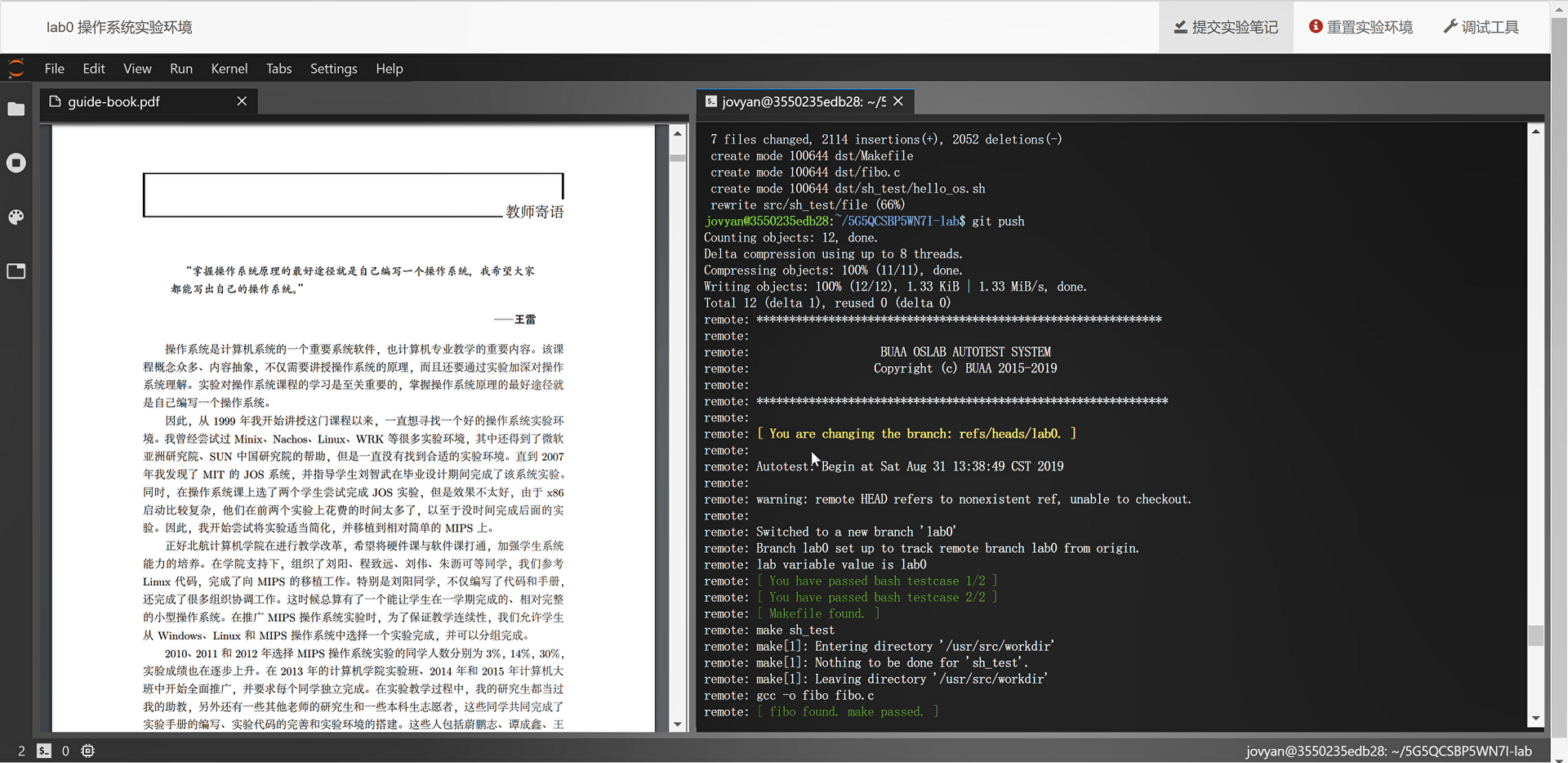

- 内核实验自动评测

-

利用git和虚拟机,实现作业自动发布、提交、编译、运行、评测,并将测试结果、可能发生错误的代码反馈给学生,整个过程不需要人工参与。

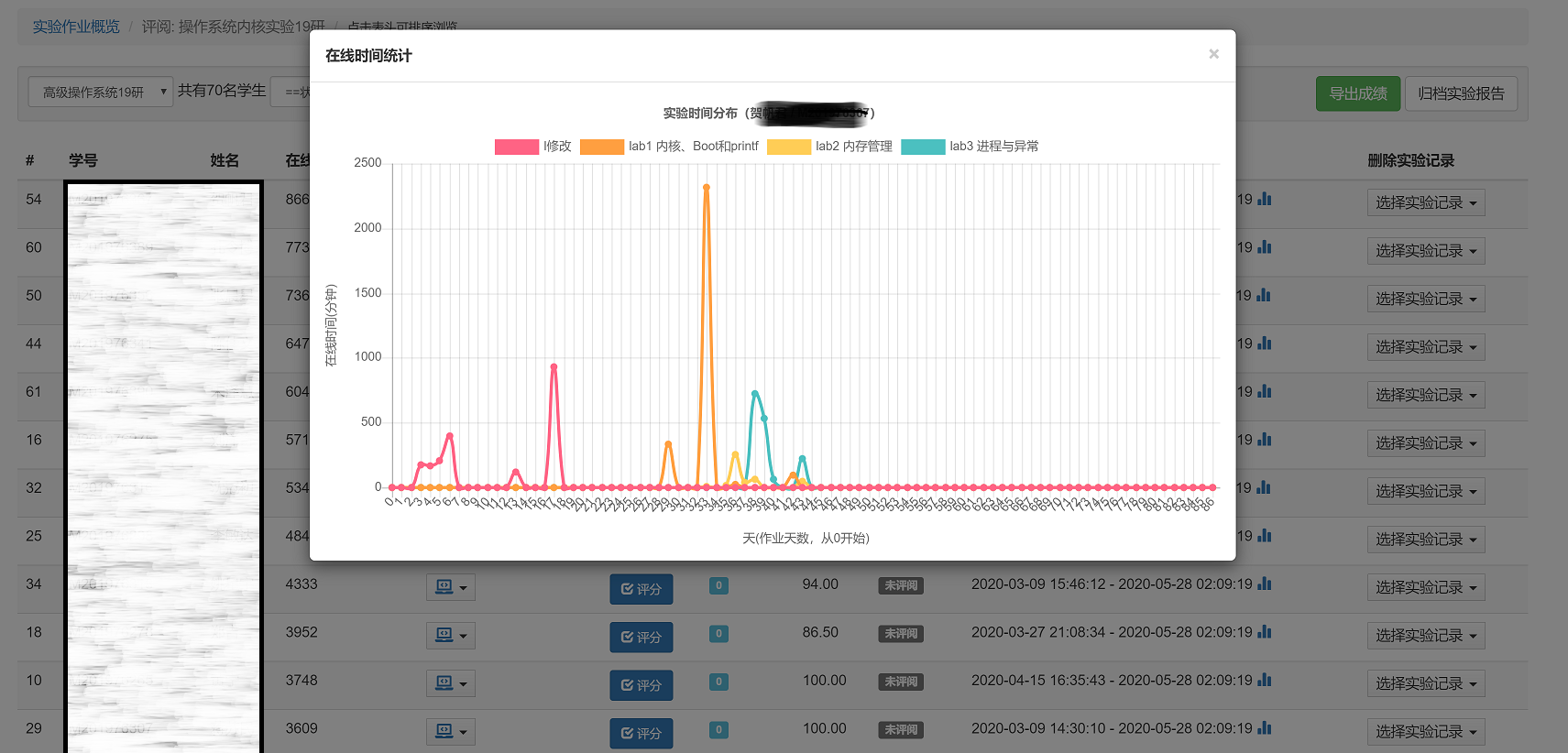

- 实验过程自动化管理

-

操作系统内核实验是一个互相衔接的体系,学生通过了某个实验评测,系统自动发布下一次实验的内容, 让有能力的同学尽早开始高难度实验,实现个体差异化培养,提升整体实验课效果。

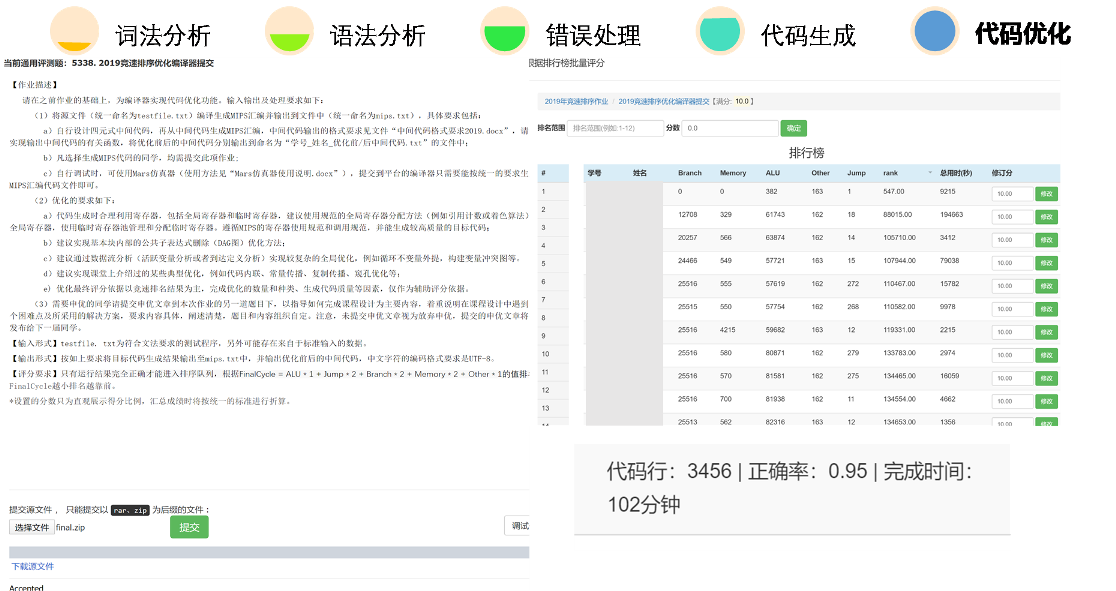

支持编译构建全过程分阶段自动评判 查看详情

学生可以从简单到复杂,最终构造出一个相对完整的小编译器。以便学生深刻地理解高级程序语言的运行机理, 理解一个完整地将高级程序设计语言编写的程序翻译为低级语言程序的过程。

实验过程全部自动化评测。

- 实验1:词法分析

-

根据给定的文法设计并实现词法分析程序。

- 实验2:语法分析

-

根据给定的文法设计并实现语法分析程序,能基于词法分析程序所识别出的单词,识别出各类语法成分。

- 实验3:错误处理

-

根据给定的文法设计并实现错误处理程序,能诊察出常见的语法和语义错误,进行错误局部化处理,并输出错误信息。

- 实验4:代码生成

-

在词法分析和语法分析的基础上,为编译器实现语义分析、代码生成功能。

- 实验5:代码优化

-

为编译器实现代码优化功能(MIPS)。

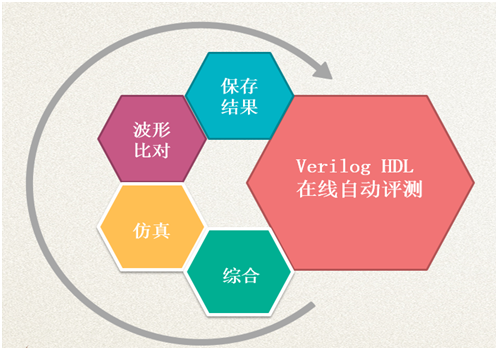

支持自动评测的计算机组成实验体系 查看详情

- Verilog HDL代码的在线自动评测

-

无须教师验收,自行记录VerilogHDL代码评测结果。

仿真波形展示,mismatch变量使得对错一目了然。

综合仿真结果输出较本地EDA平台更快。 返回综合后的标准输出,便于展开调试

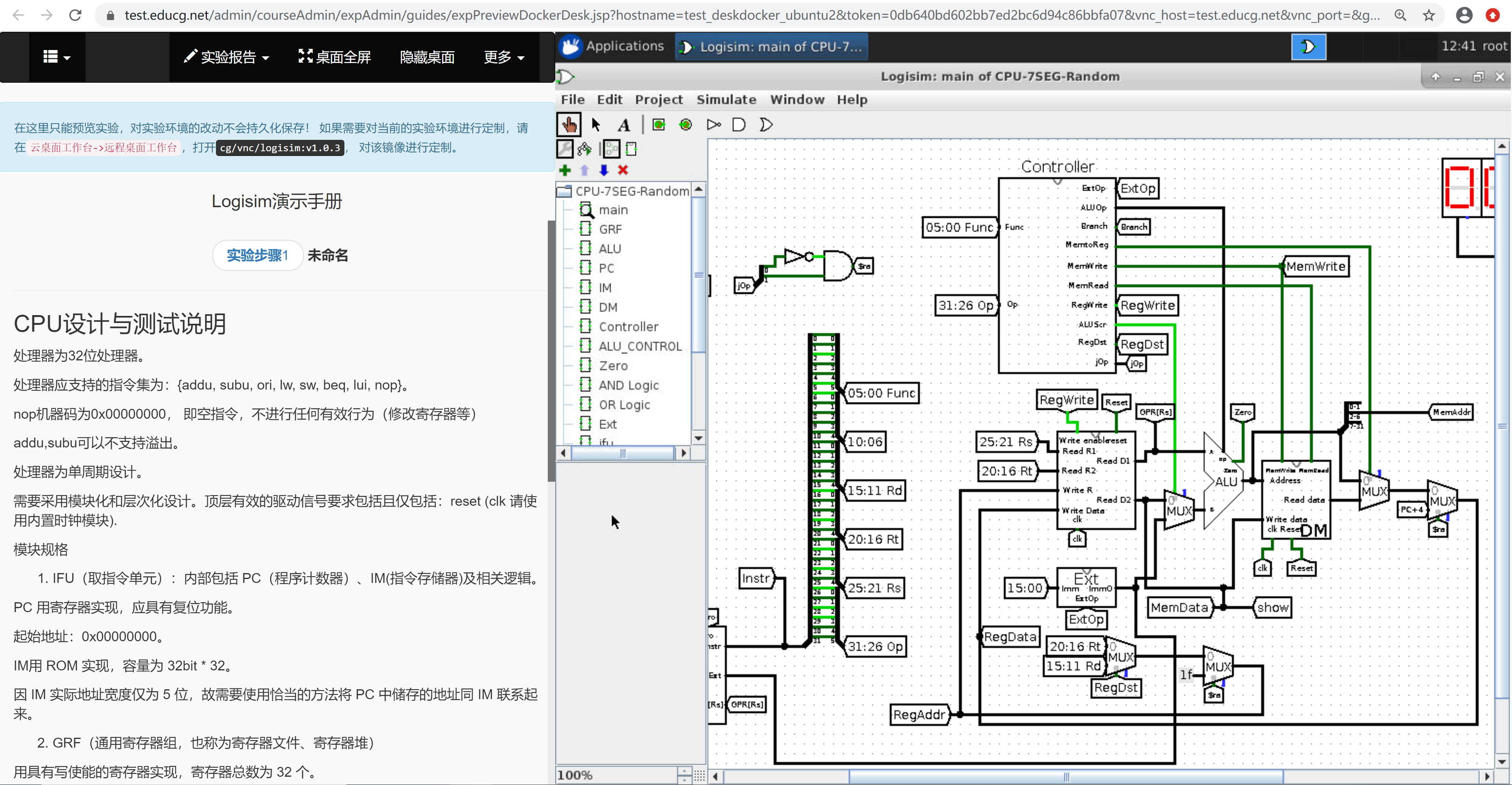

- Logisim在线实验

-

Logisim是一种用于设计和模拟数字逻辑电路的教学软件,具有界面简单、提供动态仿真等功能,有助于学生学习与逻辑电路相关的最基本概念。在Logisim中,学生能够以小规模子电路为基础逐步构建大规模数字集成电路,从而达到相关课程的实验教学目的。

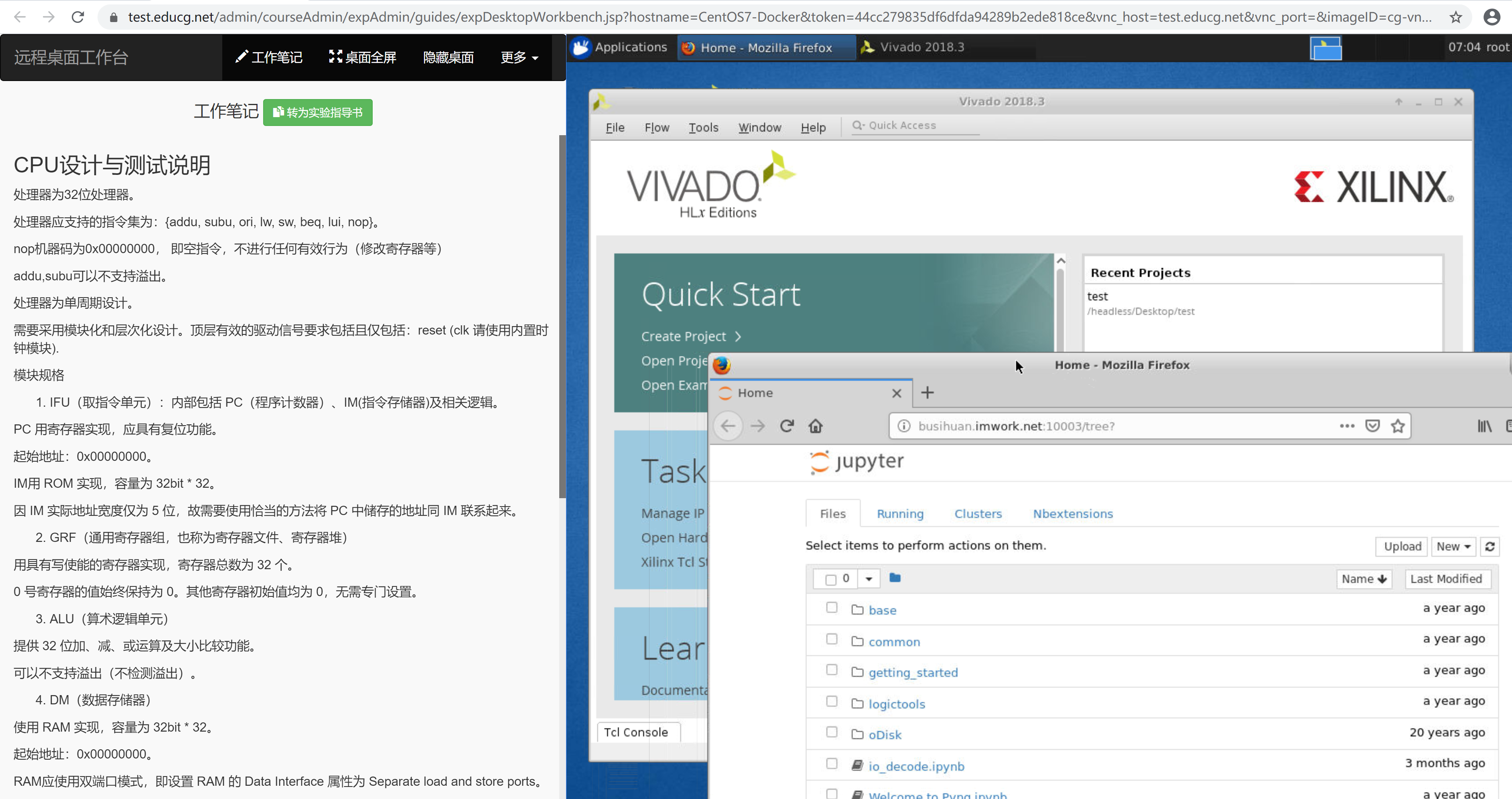

- FPGA云计算平台

-

支持私有云部署的FPGA云计算平台 通过将多块FPGA开发板高密度封装于标准化机箱中,可安装交付到高校实验室中,实现私有云部署。

与希冀云桌面实验环境无缝融合 学生在云桌面内可通过双击FPGA桌面图标,即可分配到一块FPGA硬件开发板。在做实验的过程中,学生对分配的开发板是独占的。

支持交互式使用远程硬件开发板 通过Jupyter Notebook连接远程开发板,使用Python程序交互式加载和运行比特流文件。比特流文件在FPGA上的运行结果可通过文本或者波形图的方式显示。

完备的计算机网络实验体系 查看详情

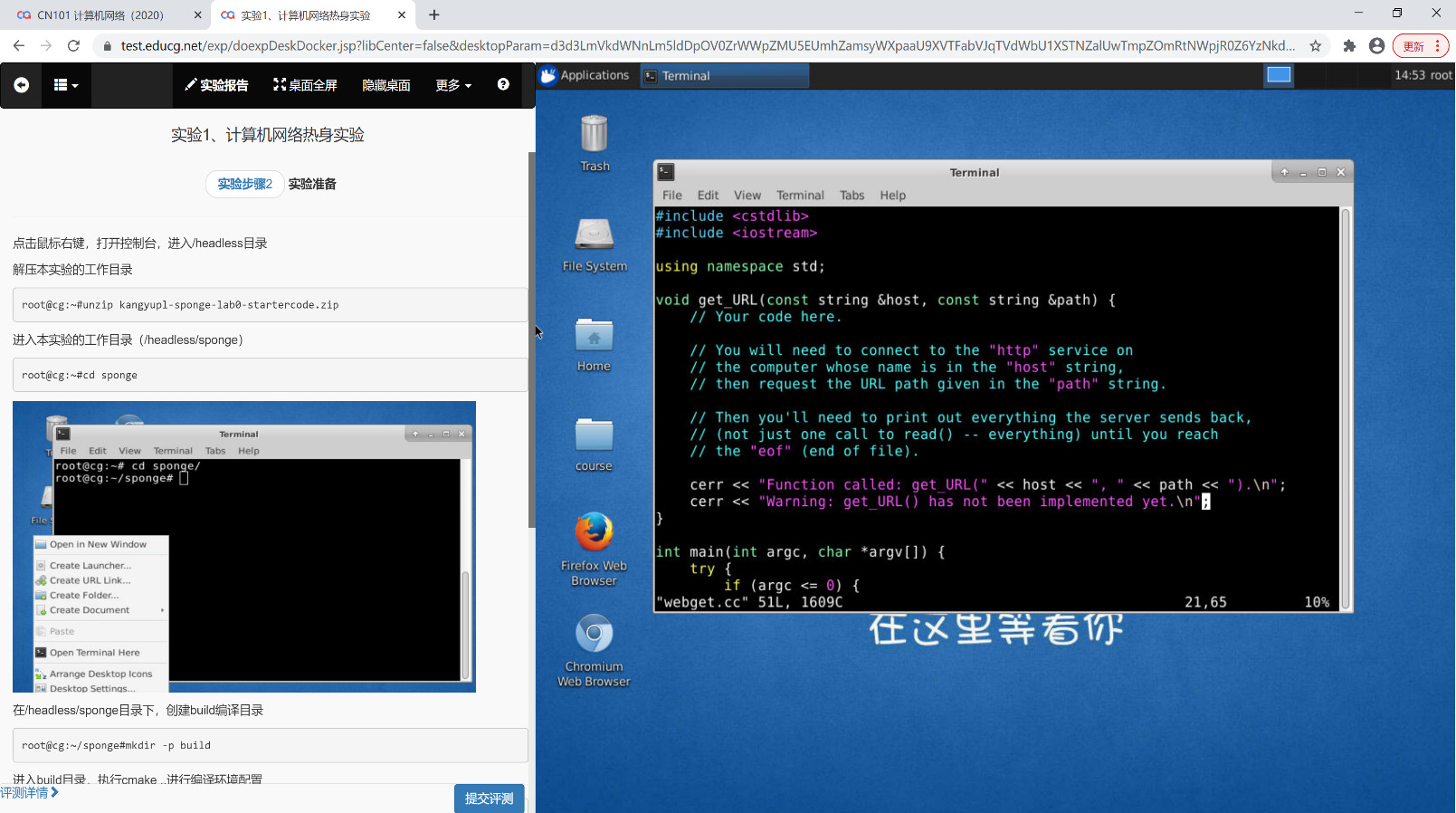

- TCP协议实现实验

-

以系统能力培养为指导,该实验体系的目标是要求学生自己动手使用C++编程实现一个真实可用的TCP协议。

按照模块化分解原则,TCP协议实现实验体系包含7个支持自动评测的实验,分别为:热身实验、实现流重组器、实现TCP接收端、实现TCP发送端、实现TCP连接、实现网络接口、实现IP路由器。

- 实验自动评测

-

为网络实验配置了自动评测脚本,学生完成实验后,点击“提交评测”按钮,可触发执行评测脚本。由评测脚本自动检测学生的网络实验环境,为学生的当前实验自动做出评价。

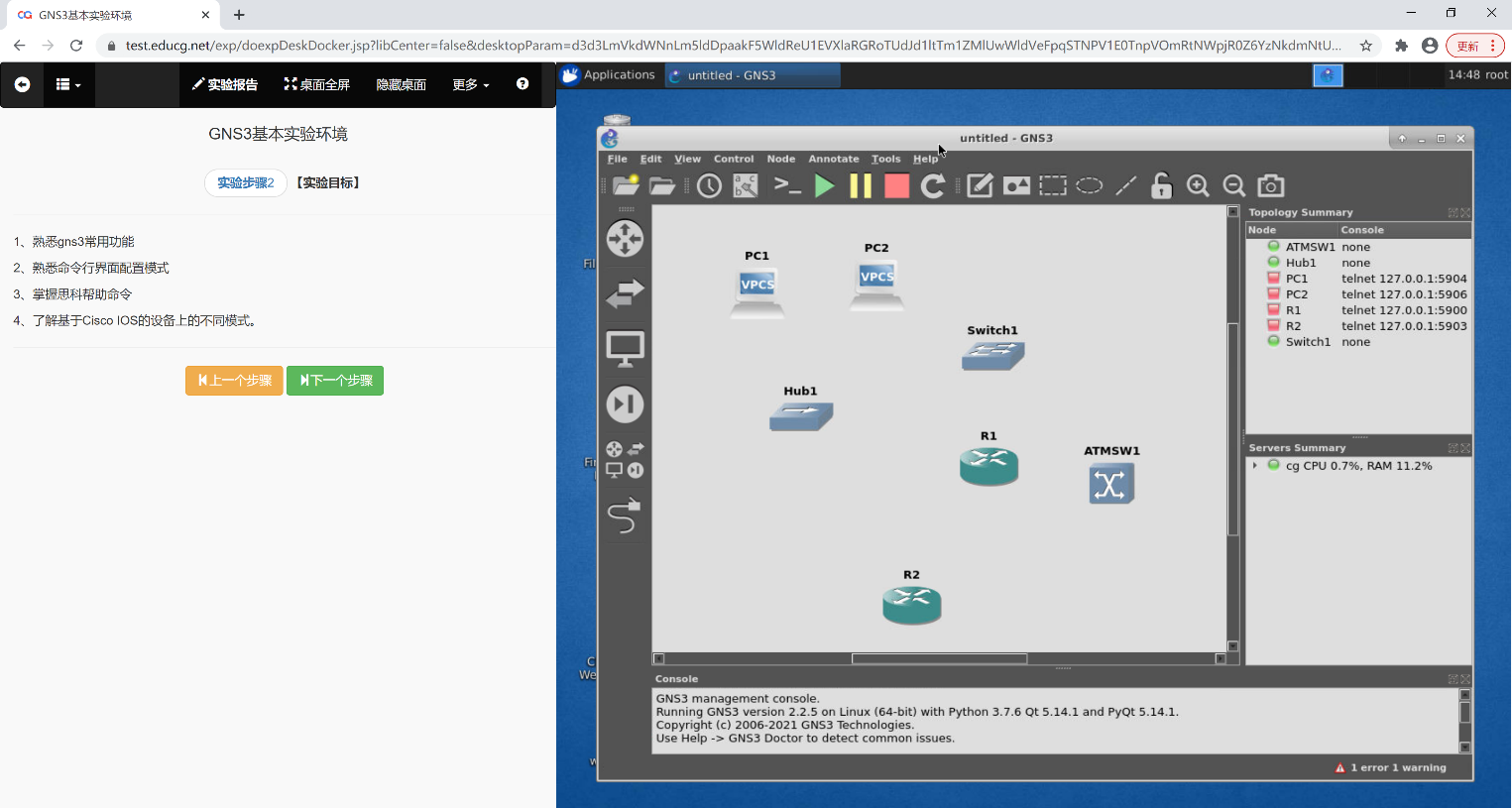

- 实验类型丰富

-

覆盖组网、协议分析、协议实现、SDN等4种不同类型的实验体系,提供计算机网络-PacketTracer、无线网络-PacketTracer、计算机网络-GNS3、TCP协议实现、Open vSwitch虚拟交换机等5类实验专题。

- 支持多种模拟器

-

通过希冀云桌面实验平台,提供GNS3、PacketTracer等多种网络模拟器实验环境。模拟器支持虚拟机、交换机和路由器的连线组网功能,通过连线组网软件提供的图形化界面,实现远程连线组网。教师也可以安装其他模拟器,支持一键保存实验环境镜像。

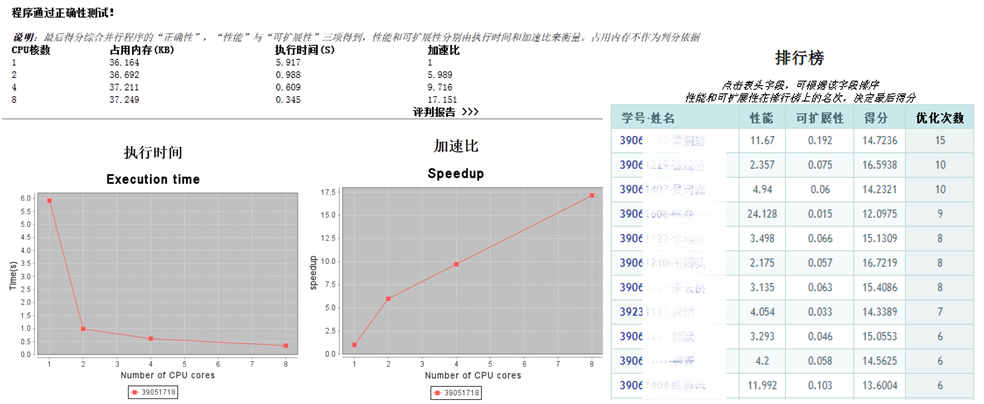

科学全面的并行计算自动评判体系 查看详情

- 正确性、性能、可扩展性三个核心指标自动评判

-

基于并行程序在真实计算环境下的运行数据,量化并行程序的正确性、性能和可扩展性三个指标,并基于量化值对并行程序自动判分。判分方法请参考“相关资料”内的论文。

- 支持多种并行语言和计算架构

-

多核多线程并行程序,包括Pthread、Java多线程、Python多线程等。MPI分布式并行程序。GPU CUDA并行程序。

- 可视化的评判结果

-

并行程序的评判结果以图表方式直观地展现,便于发现并行程序的问题并有针对性地改进,达到了人工评判无法企及的教学效果。

- 课程支持

-

高性能计算、Java多线程、并行计算、MPI程序设计、并行程序设计、并行编程原理与实践等。